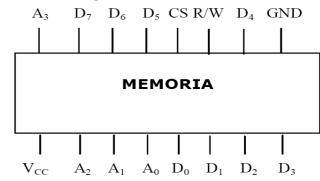

- 1.- Una cierta memoria tiene la configuración de pines que se indica en la figura adjunta. Los pines indicados con la letra A, corresponden a hilos direcciones, los indicados con la letra D a datos, y el resto corresponden a señales de control y alimentación. Deducir a partir de dicho esquema:

- a) Si se trata de una memoria ROM o RAM

- b) El número de palabras que se pueden direccionar

- c) El número de bits de cada palabra

- ci)

- 2.- Se desea diseñar un elemento aritmético que se comporte como un sumador completo de 4 bits en binario natural

- e implementar el diseño resultante mediante una memoria ROM. Se pide:

- a) El número de palabras que debe contener la memoria.

- b) El número de bits de cada palabra.

- c) El diagrama de tiempos de una operación de lectura, suponiendo que la señal de CS es activa a nivel bajo, y se produce 10 ns después de que las señales de dirección sean válidas y 15 ns antes de que las salidas de datos sean válidas.

- d) El tiempo de acceso de la memoria a partir de los datos indicados en el apartado anterior, y la frecuencia máxima de funcionamiento.

- e) Un esquema del contenido de la memoria, explicando como sería y especificando el contenido de algunas posiciones de memoria.

- 3 .- Una cierta memoria RAM de 16x4 bits, se activa mediante una señal CS a nivel alto. Las operaciones de lectura/ escritura, se controlan mediante la señal R/W (R/W=1 lectura, R/W=0 escritura) y requieren de las siguientes relaciones de temporización entre las señales involucradas en dichas operaciones:

## Ciclo de lectura:

- El retardo existente desde que la señal de validación se activa, hasta que se obtienen los datos válidos en la salida es de 90 ns.

- El retardo existente desde que se pone una nueva dirección de entrada hasta que se obtienen los datos válidos en la salida es de 90 ns (Tacc).

- Los datos permanecen válidos en la salida durante 35 ns.

- El tiempo que se mantienen los datos en la salida es 10 ns, una vez que ha cambiado la dirección o ha cesado la señal de validación (THOLD).

## Ciclo de escritura:

- El tiempo que deberán permanecer las direcciones preparadas, antes de que se active la señal de validación es de 50 ns (TSET-UP).

- El tiempo que deberán permanecer los datos a escribir preparados, antes de que se active la señal de validación es de 50 ns (TSET-UP).

- El tiempo que tarda en activarse la señal de escritura, después de que se active la señal de validación es de 150 ns.

- La anchura del pulso de escritura son 50 ns (tw).

- El tiempo de retención es nulo (tHOLD).

## Se pide:

- a) Dibujar las formas de onda, de las direcciones, señales de control y datos, que intervienen en la realización de una operación de lectura, teniendo en cuenta las relaciones de tiempos indicadas más arriba

- b) Dibujar las formas de onda que intervienen en una operación de escritura. Determinar la frecuencia máxima a la que podría realizarse esta operación.